Kompozitinis tranzistorius (Darlington ir Sziklai grandinė). Integralinės įpurškimo logikos loginiai elementai

7.2 Tranzistorius VT1

Kaip tranzistorių VT1 naudojame tranzistorių KT339A su tuo pačiu veikimo tašku kaip ir tranzistoriaus VT2:

Paimkime Rk = 100 (omų).

Apskaičiuokime atitinkamo tranzistoriaus ekvivalentinės grandinės parametrus pagal formules 5.1 - 5.13 ir 7.1 - 7.3.

Sk(req)=Sk(pass)*=2×=1,41 (pF), kur

Sk(reikalinga) - kolektoriaus sandūros talpa tam tikroje Uke0,

Sk(pasp) yra pamatinė kolektoriaus talpos Uke(pasp) vertė.

rb = 17,7 (omai); gb==0,057 (Cm), kur

atsparumas rb bazei,

Grįžtamojo ryšio kontūro konstantos atskaitos vertė.

rе= ==6,54 (omai), kur

pakartotinio skleidėjo pasipriešinimas.

gbe===1,51(mS), kur

gbe bazės emiterio laidumas,

Statinės srovės perdavimo koeficiento pamatinė vertė bendroje emiterio grandinėje.

Ce===0,803 (pF), kur

C yra emiterio talpa,

tranzistoriaus ribinio dažnio ft atskaitos vertė, kuriai esant =1

Ri= =1000 (omų), kur

Ri yra tranzistoriaus išėjimo varža,

Uke0(add), Ik0(add) - atitinkamai leistinos kolektoriaus įtampos ir pastovios kolektoriaus srovės komponento vardinės vertės.

– apkrovos pakopos įėjimo varža ir įėjimo talpa.

Viršutinis ribinis dažnis yra numatytas, kad kiekviena pakopa turi 0,75 dB iškraipymą. Ši f reikšmė atitinka technines specifikacijas. Nereikia pataisyti.

7.2.1 Terminio stabilizavimo schemos apskaičiavimas

Kaip minėta 7.1.1 punkte, šiame stiprintuve emiterio terminis stabilizavimas yra priimtiniausias, nes KT339A tranzistorius yra mažos galios, be to, emiterio stabilizavimą lengva įdiegti. Emiterio terminio stabilizavimo grandinė parodyta 4.1 pav.

Skaičiavimo procedūra:

1. Pasirinkite emiterio įtampą, daliklio srovę ir maitinimo įtampą;

2. Tada paskaičiuosime.

Daliklio srovė parenkama lygi, kur yra tranzistoriaus bazinė srovė, ir apskaičiuojama pagal formulę:

Maitinimo įtampa apskaičiuojama pagal formulę: (V)

Rezistorių vertės apskaičiuojamos pagal šias formules:

8. Įvesties grandinės įvestas iškraipymas

Kaskados įvesties grandinės schema parodyta fig. 8.1.

8.1 pav. - Kaskados įvesties grandinės schema

Jei kaskados įėjimo varža yra aproksimuota lygiagrečia RC grandine, įvesties grandinės perdavimo koeficientas aukšto dažnio srityje apibūdinamas tokia išraiška:

– kaskados įėjimo varža ir įėjimo talpa.

Įvesties grandinės reikšmė apskaičiuojama pagal (5.13) formulę, kur reikšmė pakeičiama.

9. C f, R f, C r apskaičiavimas

Stiprintuvo grandinės schemoje yra keturi jungiamieji kondensatoriai ir trys stabilizavimo kondensatoriai. Techninėse specifikacijose rašoma, kad plokščio impulso viršaus iškraipymas turi būti ne didesnis kaip 5%. Todėl kiekvienas jungiamasis kondensatorius turėtų iškraipyti plokščią impulso viršutinę dalį ne daugiau kaip 0,71%.

Plokščiojo viršaus iškraipymas apskaičiuojamas pagal formulę:

kur τ ir yra impulso trukmė.

Apskaičiuokime τ n:

τ n ir C p yra susiję su ryšiu:

kur R l, R p - varža į kairę ir į dešinę nuo talpos.

Apskaičiuokime C r. Pirmosios pakopos įėjimo varža lygi lygiagrečiai sujungtų varžų varžai: įėjimo tranzistorius, Rb1 ir Rb2.

R p = R in ||R b1 ||R b2 = 628 (Om)

Pirmosios pakopos išėjimo varža lygi lygiagrečiam ryšiui Rк ir tranzistoriaus Ri išėjimo varžai.

R l = Rк||Ri = 90,3 (omai)

R p = R in ||R b1 ||R b2 = 620 (omų)

R l = Rк||Ri = 444 (omai)

R p = R in ||R b1 ||R b2 = 48 (Om)

R l = Rк||Ri = 71 (omai)

R p = R n = 75 (omai)

kur C p1 yra atskyrimo kondensatorius tarp Rg ir pirmosios pakopos, C 12 - tarp pirmosios ir antrosios kaskados, C 23 - tarp antrosios ir trečiosios, C 3 - tarp paskutinės pakopos ir apkrovos. Pastatę visus kitus konteinerius prie 479∙10 -9 F, užtikrinsime mažesnį nei reikalaujama kritimą.

Apskaičiuokime R f ir C f (U R Ф =1V):

10. Išvada

Šiame kursiniame projekte buvo sukurtas impulsų stiprintuvas naudojant tranzistorius 2T602A, KT339A, turintis šias technines charakteristikas:

Viršutinė ribinė dažnis 14 MHz;

Stiprinimas 64 dB;

Generatoriaus ir apkrovos varža 75 Ohm;

Maitinimo įtampa 18 V.

Stiprintuvo grandinė parodyta 10.1 pav.

10.1 pav. – Stiprintuvo grandinė

Skaičiuojant stiprintuvo charakteristikas buvo naudojama ši programinė įranga: MathCad, Work Bench.

Literatūra

1. Puslaidininkiniai įtaisai. Vidutinės ir didelės galios tranzistoriai: katalogas / A.A. Zaicevas, A.I. Mirkinas, V.V. Mokryakovas ir kiti. Redagavo A.V. Golomedova.-M.: Radijas ir ryšiai, 1989.-640 p.

2. Stiprintuvo pakopų aukšto dažnio korekcijos elementų skaičiavimas naudojant dvipolius tranzistorius. Mokomasis ir metodinis kursų rengimo vadovas radijo inžinerijos specialybių studentams / A.A. Titovas, Tomskas: t. valstybė Valdymo sistemų ir radioelektronikos universitetas, 2002. - 45 p.

Dirba tiesiogiai. Darbinė linija eina per taškus Uke=Ek ir Ik=Ek÷Rn ir kerta išėjimo charakteristikų (bazinių srovių) grafikus. Norint pasiekti didžiausią amplitudę skaičiuojant impulsų stiprintuvą, darbo taškas buvo pasirinktas arčiau žemiausio įtampos, nes paskutinėje stadijoje impulsas bus neigiamas. Pagal išėjimo charakteristikų grafiką (1 pav.) buvo rastos reikšmės IKpost = 4,5 mA, ....

Sf, Rf apskaičiavimas, trečiadienis 10. Išvada Literatūra TECHNINĖ UŽDUOTIS Nr. Projekto tema: Impulsų stiprintuvas Generatoriaus varža Rg = 75 Ohm. Stiprinimas K = 25 dB. Impulso trukmė 0,5 μs. Poliškumas yra „teigiamas“. Darbo koeficientas 2. Nustūmimo laikas 25 ns. Paleisti...

Kad norint suderinti su apkrovos varža, po stiprinimo etapų reikia sumontuoti emiterio sekiklį, nubraižykime stiprintuvo grandinę: 2.2 Stiprintuvo statinio režimo skaičiavimas Apskaičiuojame pirmąją stiprinimo pakopą. Parenkame darbo tašką pirmajai stiprintuvo pakopai. Jo savybės:...

Įvesties signalo šaltinio varža, taigi ir optimalumo sąlygos keitimas švitinimo metu, nesukelia papildomo triukšmo padidėjimo. Radiacijos poveikis IOU. AI įtaka IOU parametrams. Integruoti operaciniai stiprintuvai (IOA) – tai aukštos kokybės preciziniai stiprintuvai, priklausantys universalių ir daugiafunkcinių analoginių...

Jei paimtume, pavyzdžiui, tranzistorių MJE3055T jo maksimali srovė yra 10A, o stiprinimas yra tik apie 50; atitinkamai, kad jis visiškai atsidarytų, į bazę reikia pumpuoti apie du šimtus miliamperų srovės. Įprasta MK išvestis tiek neatlaikys, bet jei tarp jų prijungsite silpnesnį tranzistorių (kažkokį BC337), galintį ištraukti šį 200 mA, tada tai lengva. Bet tai tam, kad jis žinotų. O jei iš improvizuotų šiukšlių teks pasidaryti valdymo sistemą – pravers.

Praktiškai paruoštas tranzistorių mazgai. Išoriškai jis nesiskiria nuo įprasto tranzistoriaus. Tas pats kūnas, tos pačios trys kojos. Tiesiog jis turi daug galios, o valdymo srovė mikroskopinė :) Kainynuose dažniausiai nesivargina ir rašo paprastai - Darlington tranzistorius arba kompozitinis tranzistorius.

Pavyzdžiui, pora BDW93C(NPN) ir BDW94С(PNP) Štai jų vidinė struktūra iš duomenų lapo.

Be to, yra Darlingtono asamblėjos. Kai į vieną pakuotę iš karto supakuotos kelios. Nepakeičiamas dalykas, kai reikia valdyti galingą LED ekraną arba žingsninį variklį (). Puikus tokio pastatymo pavyzdys – labai populiarus ir lengvai prieinamas ULN2003, galintis vilkti iki 500 mA kiekvienam iš septynių mazgų. Galimi išėjimai įtraukti lygiagrečiai padidinti srovės ribą. Iš viso vienas ULN gali pernešti net 3,5 A, jei visi jo įėjimai ir išėjimai yra lygiagretūs. Mane džiugina tai, kad išėjimas yra priešais įėjimą, po juo labai patogu nukreipti lentą. Tiesiogiai.

Duomenų lape parodyta šio lusto vidinė struktūra. Kaip matote, čia taip pat yra apsauginių diodų. Nepaisant to, kad jie nupiešti tarsi operaciniai stiprintuvai, čia išėjimas yra atviro kolektoriaus tipo. Tai yra, jis gali tik trumpąjį jungimą į žemę. Kas paaiškėja iš to paties duomenų lapo, jei pažvelgsite į vieno vožtuvo struktūrą.

Fig. 2.16 paveiksle parodyta loginio elemento su indukuotu n tipo kanalu schema (vadinamoji n MIS technologija). Pagrindiniai tranzistoriai VT 1 ir VT 2 sujungti nuosekliai, tranzistorius VT 3 veikia kaip apkrova. Tuo atveju, kai abiejuose elemento įėjimuose yra taikoma aukšta įtampa U 1 (x 1 = 1, x 2 = 1), abu tranzistoriai VT 1 ir VT 2 yra atviri, o išėjime nustatoma žema įtampa U 0. Visais kitais atvejais bent vienas iš tranzistorių VT 1 arba VT 2 yra uždarytas, o išėjime nustatyta įtampa U 1. Taigi elementas atlieka loginę AND-NE funkciją.

Fig. 2.17 paveiksle parodyta elemento OR-NOT schema. Jo išėjime nustatoma žema įtampa U 0, jei bent vienas iš įėjimų turi aukštą įtampą U 1, atidarant vieną iš pagrindinių tranzistorių VT 1 ir VT 2.

Parodyta pav. 2.18 diagrama yra KMDP technologijos elemento NOR-NOT diagrama. Jame tranzistoriai VT 1 ir VT 2 yra pagrindiniai, tranzistoriai VT 3 ir VT 4 – apkrovos. Tegul aukšta įtampa U1. Šiuo atveju tranzistorius VT 2 yra atidarytas, tranzistorius VT 4 uždarytas ir, nepriklausomai nuo įtampos lygio kitoje įėjime ir likusių tranzistorių būsenos, išėjime nustatoma žema įtampa U 0. Elementas įgyvendina loginę OR-NOT operaciją.

CMPD grandinė pasižymi labai mažu srovės suvartojimu (taigi ir galia) iš maitinimo šaltinių.

Integralinės įpurškimo logikos loginiai elementai

Fig. 2.19 paveiksle parodyta integralinio įpurškimo logikos loginio elemento topologija (I 2 L). Tokiai struktūrai sukurti reikalingos dvi difuzijos n tipo laidumo silicyje fazės: pirmosios fazės metu susidaro sritys p 1 ir p 2, o antrosios fazės metu – n 2 sritys.

Elementas turi struktūrą p 1 -n 1 -p 2 -n 1 . Tokią keturių sluoksnių struktūrą patogu įsivaizduoti kaip dviejų įprastų trijų sluoksnių tranzistorių struktūrų jungtį:

p 1 -n 1 -p 2 n 1 -p 2 -n 1

Šį vaizdą atitinkanti diagrama parodyta 2.20 pav., a. Panagrinėkime elemento veikimą pagal šią schemą.

Tranzistorius VT 2, kurio struktūra yra n 1 -p 2 -n 1 tipo, atlieka keitiklio funkcijas su keliais išėjimais (kiekvienas kolektorius sudaro atskirą elemento išėjimą pagal atviro kolektoriaus grandinę).

Tranzistorius VT 2, vadinamas purkštukas, turi tokią struktūrą kaip p 1 -n 1 -p 2 . Kadangi šių tranzistorių plotas n 1 yra bendras, tranzistoriaus VT 2 emiteris turi būti prijungtas prie tranzistoriaus VT 1 pagrindo; dėl bendros zonos p 2 reikia prijungti tranzistoriaus VT 2 pagrindą su tranzistoriaus VT 1 kolektoriumi. Taip sukuriamas ryšys tarp tranzistorių VT 1 ir VT 2, parodytas 2.20a pav.

Kadangi tranzistoriaus VT 1 emiteris turi teigiamą potencialą, o bazės potencialas yra nulinis, emiterio sandūra yra nukreipta į priekį, o tranzistorius yra atviras.

Šio tranzistoriaus kolektoriaus srovė gali būti uždaryta per tranzistorių VT 3 (ankstesnio elemento keitiklį) arba per tranzistoriaus VT 2 emiterio jungtį.

Jei ankstesnis loginis elementas yra atviroje būsenoje (tranzistorius VT 3 yra atidarytas), tada šio elemento įėjime yra žemos įtampos lygis, kuris, veikdamas VT 2 pagrindu, išlaiko šį tranzistorių uždaroje būsenoje. Injektoriaus srovė VT 1 uždaroma per tranzistorių VT 3. Uždarius ankstesnį loginį elementą (uždarytas tranzistorius VT 3), purkštuko VT 1 kolektoriaus srovė patenka į tranzistoriaus VT 2 pagrindą, o šis tranzistorius yra nustatytas į atvirą būseną.

Taigi, kai VT 3 yra uždarytas, tranzistorius VT 2 yra atidarytas ir, atvirkščiai, kai VT 3 yra atidarytas, tranzistorius VT 2 yra uždarytas. Elemento atviroji būsena atitinka log.0 būseną, o uždara – log.1 būseną.

Injektorius yra nuolatinės srovės šaltinis (kuri gali būti bendra elementų grupei). Dažnai jie naudoja įprastą grafinį elemento žymėjimą, pateiktą Fig. 2.21, gim.

Fig. 2.21a paveiksle parodyta grandinė, kuri įgyvendina operaciją OR-NOT. Elementų kolektorių pajungimas atitinka vadinamųjų veikimą montavimas I. Iš tiesų, pakanka, kad bent vienas elementas būtų atviroje būsenoje (log.0 būsena), tada kito elemento purkštuko srovė bus uždaryta per atvirą keitiklį ir bus nustatytas žemas log.0 lygis ties bendra elementų išvestis. Vadinasi, šioje išvestyje suformuojama reikšmė, atitinkanti loginę išraišką x 1 · x 2. Jai pritaikius de Morgano transformaciją gaunama išraiška x 1 · x 2 = . Todėl šis elementų sujungimas tikrai įgyvendina OR-NOT operaciją.

Loginiai elementai IR 2 L turi šiuos privalumus:

užtikrinti aukštą integracijos laipsnį; gaminant I 2 L grandines naudojami tie patys technologiniai procesai kaip ir gaminant integrines grandynas ant bipolinių tranzistorių, tačiau technologinių operacijų ir reikalingų fotokaukių skaičius mažesnis;

naudojama sumažinta įtampa (apie 1 V);

suteikti galimybę keistis galia įvairiais našumo diapazonais (galios suvartojimas gali būti keičiamas keliomis eilėmis, o tai atitinkamai pakeis našumą);

yra gerai suderinami su TTL elementais.

Fig. 2.21b paveiksle parodyta perėjimo iš I 2 L elementų į TTL elementą schema.

Pagrindinis loginis serijos elementas yra AND-NE loginis elementas. Fig. 2.3 paveiksle parodytos trijų pradinių NAND TTL elementų diagramos. Visose grandinėse yra trys pagrindiniai etapai: tranzistoriaus įvestis VT1, įgyvendinantis loginę AND funkciją; fazių atskyrimo tranzistorius VT2 ir „push-pull“ išėjimo pakopa.

2.3.a pav. K131 serijos pagrindinio elemento schema

K131 serijos loginio elemento veikimo principas (2.3.a pav.) yra toks: kai kuriame nors iš įėjimų gaunamas žemo lygio signalas (0 - 0,4V), daugiafunkcinio pagrindo-emiterio sandūra. -emiterio tranzistorius VT1 yra nukreiptas į priekį (atrakintas), o beveik visa srovė, tekanti per rezistorių R1, yra išsišakojusi į žemę, dėl to VT2 užsidaro ir veikia išjungimo režimu. Srovė, tekanti per rezistorių R2, prisotina tranzistoriaus VT3 bazę. Tranzistoriai VT3 ir VT4, sujungti pagal Darlingtono grandinę, sudaro sudėtinį tranzistorių, kuris yra emiterio sekėjas. Jis veikia kaip išvesties pakopa signalo galiai sustiprinti. Grandinės išvestyje generuojamas aukšto loginio lygio signalas.

Jei į visus įėjimus tiekiamas aukšto lygio signalas, kelių emiterių tranzistoriaus VT1 bazinio emiterio jungtis yra uždarame režime. Srovė, tekanti per rezistorių R1, prisotina tranzistoriaus VT1 bazę, dėl to tranzistorius VT5 atrakinamas ir grandinės išvestyje nustatomas loginis nulinis lygis.

Kadangi perjungimo momentu tranzistoriai VT4 ir VT5 yra atviri ir per juos teka didelė srovė, į grandinę įvedamas ribojantis rezistorius R5.

VT2, R2 ir R3 sudaro fazių atskyrimo kaskadą. Būtina po vieną įjungti išvesties n-p-n tranzistorius. Kaskadoje yra du išėjimai: kolektorius ir emiteris, kurių signalai yra priešfaziniai.

Diodai VD1 - VD3 yra apsauga nuo neigiamų impulsų.

2.3.b, c pav. K155 ir K134 serijų pagrindinių elementų scheminės diagramos

K155 ir K134 serijų mikroschemose išėjimo pakopa yra pastatyta ant nesudėtinio kartotuvo (tik tranzistoriaus VT3) ir prisotintą tranzistorių VT5įvedus lygio poslinkio diodą VD4(2.3 pav., b, c). Paskutiniai du etapai sudaro sudėtingą keitiklį, kuris įgyvendina loginę NOT operaciją. Jei įvesite du fazių atskyrimo etapus, bus įdiegta funkcija OR-NOT.

Fig. 2.3, ir rodomas pagrindinis K131 serijos loginis elementas (užsienio analogas – 74N). Pagrindinis K155 serijos elementas (užsienio analogas - 74) parodytas pav. 2.3, b, a pav. 2.3, c - K134 serijos elementas (užsienio analogas - 74L). Dabar šios serijos praktiškai nėra sukurtos.

Pradinės plėtros TTL mikroschemos pradėjo aktyviai keisti TTLSh mikroschemomis, kurių vidinėje struktūroje yra jungtys su Schottky barjeru. Šotkio sandūros tranzistorius (Schottky tranzistorius) pagrįstas gerai žinoma nesočiojo tranzistoriaus jungiklio grandine (2.4.a pav.).

2.4 pav. Struktūros gavimo su Šotkio perėjimu principo paaiškinimas:

a - nesočiųjų tranzistorių jungiklis; b - tranzistorius su Schottky diodu; c - Šotkio tranzistoriaus simbolis.

Kad tranzistorius nepatektų į sodrumą, tarp kolektoriaus ir pagrindo prijungiamas diodas. Naudoti grįžtamojo ryšio diodą tranzistoriaus prisotinimui pašalinti pirmasis pasiūlė B. N. Kononovas.Tačiau šiuo atveju jis gali padidėti iki 1 V. Idealus diodas yra Šotkio barjerinis diodas. Tai kontaktas, susidarantis tarp metalo ir lengvai legiruoto n-puslaidininkio. Metale tik dalis elektronų yra laisvi (esantys už valentinės zonos). Puslaidininkyje laisvieji elektronai egzistuoja prie laidumo ribos, susidariusios pridedant priemaišų atomų. Nesant poslinkio įtampos, elektronų, kertančių barjerą iš abiejų pusių, skaičius yra vienodas, t.y., nėra srovės. Į priekį nukreipti elektronai turi energijos, kad galėtų pereiti potencialo barjerą ir patekti į metalą. Didėjant poslinkio įtampai, barjero plotis mažėja, o tiesioginė srovė greitai didėja.

Esant atvirkštiniam poslinkiui, puslaidininkio elektronams reikia daugiau energijos, kad įveiktų potencialo barjerą. Metalo elektronams potencialo barjeras nepriklauso nuo poslinkio įtampos, todėl teka nedidelė atvirkštinė srovė, kuri išlieka praktiškai pastovi, kol įvyksta lavina.

Srovę Schottky dioduose lemia daugumos nešikliai, todėl ji yra didesnė esant tokiam pačiam tiesioginiam poslinkiui, todėl tiesioginis įtampos kritimas per Šotkio diodą yra mažesnis nei įprastoje p-n sandūroje, esant tam tikrai srovei. Taigi, Schottky diodo slenkstinė atidarymo įtampa yra (0,2–0,3) V, priešingai nei įprastinio silicio diodo slenkstinė įtampa, kuri yra 0,7 V, ir žymiai sumažina puslaidininkio mažumos nešlių tarnavimo laiką.

Pav. diagramoje. 2.4, b tranzistorius VT1 Nepersotina Shatky diodas su žemu atidarymo slenksčiu (0,2...0,3) V, todėl įtampa šiek tiek padidės, palyginti su prisotintu tranzistoriumi VT1. Fig. 2.4, c rodoma grandinė su „Schottky tranzistoriumi“. Remiantis Schottky tranzistoriais, buvo pagamintos dviejų pagrindinių TTLSh serijų mikroschemos (2.5 pav.)

Fig. 2.5, ir parodyta didelės spartos loginio elemento, naudojamo kaip K531 serijos mikroschemų pagrindas (užsienio analogas - 74S), diagrama (S yra pradinė vokiečių fiziko Schottky pavardės raidė). Šiame elemente fazių atskyrimo kaskados emiterio grandinė pagaminta ant tranzistoriaus VT2, įjungtas srovės generatorius - tranzistorius VT6 su rezistoriais R4 Ir R5. Tai leidžia padidinti loginio elemento našumą. Priešingu atveju šis loginis elementas yra panašus į pagrindinį K131 serijos elementą. Tačiau Schottky tranzistorių įvedimas leido sumažinti tzd.r padvigubėjo.

Fig. 2.5, b rodo pagrindinio K555 serijos loginio elemento diagramą (užsienio analogas - 74LS). Šioje grandinėje vietoj kelių emiterių tranzistoriaus įėjime naudojama Schottky diodų matrica. „Shatky“ diodų įvedimas pašalina perteklinių bazinių įkrovų kaupimąsi, dėl kurių padidėja tranzistoriaus išjungimo laikas, ir užtikrinamas perjungimo laiko stabilumas temperatūros diapazone.

Išėjimo pakopos viršutinės svirties rezistorius R6 sukuria reikiamą įtampą tranzistoriaus pagrindu VT3 kad jį atidarytumėte. Norėdami sumažinti energijos suvartojimą, kai vartai yra uždaryti (), rezistorius R6 jungtis ne prie bendros magistralės, o prie elemento išvesties.

Diodas VD7, sujungtas nuosekliai su R6 ir lygiagrečiai fazių atskyrimo kaskados kolektoriaus apkrovos rezistoriui R2, leidžia sumažinti grandinės įjungimo delsą naudojant dalį apkrovos talpoje sukauptos energijos, kad padidintų tranzistoriaus kolektoriaus srovę VT1 pereinamuoju režimu.

Tranzistorius VT3 yra įgyvendintas be Schottky diodų, nes veikia aktyviu režimu (emiterio sekėjas).

Sudėtinis tranzistorius (Darlingtono tranzistorius) - dviejų ar daugiau bipolinių tranzistorių sujungimas, siekiant padidinti srovės stiprinimą. Toks tranzistorius naudojamas grandinėse, kurios veikia didelėmis srovėmis (pavyzdžiui, įtampos stabilizatoriaus grandinėse, galios stiprintuvų išėjimo pakopose) ir stiprintuvų įvesties pakopose, jei reikia užtikrinti didelę įėjimo varžą.

Sudėtinio tranzistoriaus simbolis

Sudėtinis tranzistorius turi tris gnybtus (bazę, emiterį ir kolektorių), kurie yra lygiaverčiai įprasto vieno tranzistoriaus gnybtams. Tipiško sudėtinio tranzistoriaus (kartais klaidingai vadinamo „superbeta“) srovės stiprinimas didelės galios tranzistorių atveju yra ≈ 1000, o mažos galios tranzistorių – ≈ 50 000. Tai reiškia, kad sudėtiniam tranzistoriui įjungti pakanka nedidelės bazinės srovės.

Skirtingai nuo bipolinių tranzistorių, lauko tranzistoriai nenaudojami sudėtiniame jungtyje. Nereikia derinti lauko tranzistorių, nes jie jau turi itin mažą įėjimo srovę. Tačiau yra grandinių (pavyzdžiui, izoliuotų vartų dvipolis tranzistorius), kuriose lauko efekto ir bipoliniai tranzistoriai naudojami kartu. Tam tikra prasme tokios grandinės taip pat gali būti laikomos sudėtiniais tranzistoriais. Tas pats ir kompozitiniam tranzistoriuiGalima padidinti stiprinimo vertę sumažinus pagrindo storį, tačiau tai kelia tam tikrų technologinių sunkumų.

Pavyzdys superbeta (super-β)tranzistoriai gali būti naudojami KT3102, KT3107 serijose. Tačiau juos taip pat galima derinti naudojant Darlingtono schemą. Šiuo atveju bazinė poslinkio srovė gali būti lygi tik 50 pA (tokių grandinių pavyzdžiai yra operaciniai stiprintuvai, tokie kaip LM111 ir LM316).

Tipiško stiprintuvo, naudojant sudėtinius tranzistorius, nuotrauka

Darlingtono grandinė

Vieną tokių tranzistorių rūšį išrado elektros inžinierius Sidney Darlingtonas.

Sudėtinio tranzistoriaus schema

Sudėtinis tranzistorius yra pakopinis kelių tranzistorių, sujungtų taip, kad apkrova ankstesnės pakopos emiteryje yra kitos pakopos tranzistoriaus bazės-emiterio perėjimas, tai yra, tranzistoriai yra sujungti kolektoriais ir įėjimo tranzistoriaus emiteris yra prijungtas prie išėjimo tranzistoriaus pagrindo. Be to, pirmojo tranzistoriaus varžinė apkrova gali būti naudojama kaip grandinės dalis, siekiant pagreitinti uždarymą. Toks ryšys kaip visuma laikomas vienu tranzistoriumi, kurio srovės stiprinimas, kai tranzistoriai veikia aktyviu režimu, yra maždaug lygus pirmojo ir antrojo tranzistorių stiprinimo sandaugai:

β с = β 1 ∙ β 2

Parodykime, kad sudėtinis tranzistorius iš tikrųjų turi koeficientąβ , žymiai didesnis už abu jo komponentus. Prieaugio nustatymasdlb=dlb1, mes gauname:

dle1 = (1 + β 1) ∙ dlb=dlb2

dlĮ=dlk1+dlk2= β 1 ∙ dlb+ β 2 ∙ ((1 + β 1) ∙ dlb)

Dalijimasis dl ikiįjungta dlb, randame gautą diferencialinį perdavimo koeficientą:

β Σ = β 1 + β 2 + β 1 ∙ β 2

Nes visadaβ >1 , galima būtų svarstyti:

β Σ = β 1 ∙ β 1

Reikia pabrėžti, kad koeficientaiβ 1 Ir β 1 gali skirtis net ir to paties tipo tranzistorių atveju, nes emiterio srovėaš e2 V 1 + β 2kartų didesnė už emiterio srovęaš e1(tai išplaukia iš akivaizdžios lygybėsI b2 = I e1).

Siklų schema

Darlingtono pora yra panaši į Sziklai tranzistorių jungtį, pavadintą jos išradėjo George'o Sziklai vardu, taip pat kartais vadinama papildomu Darlingtono tranzistoriumi. Skirtingai nuo Darlingtono grandinės, kurią sudaro du to paties laidumo tipo tranzistoriai, Sziklai grandinėje yra skirtingų poliškumo tranzistorių ( p – n – p ir n – p – n ). Siklų pora elgiasi kaip n–p–n - tranzistorius su dideliu stiprėjimu. Įvesties įtampa yra įtampa tarp tranzistoriaus Q1 bazės ir emiterio, o soties įtampa yra lygi bent įtampos kritimui per diodą. Tarp tranzistoriaus Q2 pagrindo ir emiterio rekomenduojama įtraukti mažos varžos rezistorių. Ši grandinė naudojama galinguose „push-pull“ išėjimo etapuose, kai naudojami to paties poliškumo išvesties tranzistoriai.

Sziklai kaskados, panašios į tranzistorių su n – p – n perėjimas

Kaskodo grandinė

Sudėtinis tranzistorius, pagamintas pagal vadinamąją kaskodinę grandinę, pasižymi tuo, kad tranzistorius VT1 yra sujungtas į grandinę su bendru emiteriu, o tranzistorius VT2 - į grandinę su bendra baze. Toks sudėtinis tranzistorius yra lygiavertis vienam tranzistoriui, sujungtam į bendro emiterio grandinę, tačiau jis turi daug geresnes dažnio savybes ir didesnę neiškraipytą apkrovos galią, taip pat gali žymiai sumažinti Millerio efektą (padidėja lygiavertė įrenginio talpa). invertuojantis stiprintuvo elementas dėl grįžtamojo ryšio iš išėjimo į šio elemento įvestį, kai jis išjungtas).

Kompozitinių tranzistorių privalumai ir trūkumai

Didelės kompozitinių tranzistorių stiprinimo vertės realizuojamos tik statiniu režimu, todėl kompozitiniai tranzistoriai plačiai naudojami operacinių stiprintuvų įvesties etapuose. Aukšto dažnio grandinėse kompozitiniai tranzistoriai nebeturi tokių pranašumų - ribinis srovės stiprinimo dažnis ir sudėtinių tranzistorių veikimo greitis yra mažesnis už tuos pačius kiekvieno tranzistoriaus VT1 ir VT2 parametrus.

Privalumai:

A)Didelis srovės stiprinimas.

b)Darlingtono grandinė gaminama integrinių grandynų pavidalu, o esant tokiai pačiai srovei, silicio darbinis paviršius yra mažesnis nei bipolinių tranzistorių. Šios grandinės yra labai įdomios esant aukštai įtampai.

Trūkumai:

A)Mažas našumas, ypač perėjimas iš atviros į uždarą būseną. Dėl šios priežasties kompozitiniai tranzistoriai pirmiausia naudojami žemo dažnio raktų ir stiprintuvų grandinėse, aukštuose dažniuose jų parametrai yra prastesni nei vieno tranzistoriaus.

b)Tiesioginis įtampos kritimas per bazinio emiterio sandūrą Darlingtono grandinėje yra beveik dvigubai didesnis nei įprasto tranzistoriaus, o silicio tranzistorių – apie 1,2–1,4 V (negali būti mažesnis nei dvigubai didesnis nei įtampos kritimas p-n sandūroje). .

V)Aukšta kolektoriaus-emiterio soties įtampa, silicio tranzistoriui apie 0,9 V (palyginti su 0,2 V įprastų tranzistorių), mažos galios tranzistoriams ir apie 2 V didelės galios tranzistoriams (negali būti mažesnė už įtampos kritimą per p-n jungtį plius įtampos kritimas per sočiųjų įvesties tranzistorių).

Apkrovos rezistoriaus R1 naudojimas leidžia pagerinti kai kurias sudėtinio tranzistoriaus charakteristikas. Rezistoriaus vertė parenkama taip, kad tranzistoriaus VT1 kolektoriaus-emiterio srovė uždaroje būsenoje sukurtų įtampos kritimą rezistoriuje, kurio nepakanka tranzistoriaus VT2 atidarymui. Taigi tranzistoriaus VT1 nuotėkio srovė nestiprinama tranzistoriaus VT2, todėl sumažėja bendra kompozitinio tranzistoriaus kolektoriaus-emiterio srovė išjungtoje būsenoje. Be to, rezistoriaus R1 naudojimas padeda padidinti sudėtinio tranzistoriaus greitį, priverčiant uždaryti tranzistorių VT2. Paprastai R1 varža yra šimtai omų didelės galios Darlingtono tranzistoriuje ir keli kOhm mažo signalo Darlingtono tranzistoriuje. Grandinės su emiterio rezistoriumi pavyzdys yra galingas n-p-n Darlington tranzistorius, tipas KT825, jo srovės stiprinimas yra 10 000 (tipinė vertė), kai kolektoriaus srovė yra 10 A.

Istorija apie lakūnus, kurie bombardavo Hirosimą ir Nagasakį

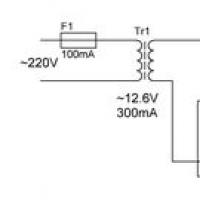

Istorija apie lakūnus, kurie bombardavo Hirosimą ir Nagasakį Sklandus talpos įkrovimas: ką pasirinkti?

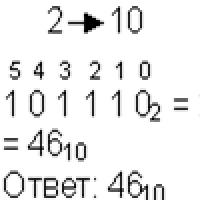

Sklandus talpos įkrovimas: ką pasirinkti? Mažasis matematikos fakultetas

Mažasis matematikos fakultetas „Kodėl sapne svajojate apie apvalų šokį?

„Kodėl sapne svajojate apie apvalų šokį? Kodėl svajojate apie bažnyčią viduje: sapno prasmės aiškinimas pagal įvairias svajonių knygas vyrams ir moterims

Kodėl svajojate apie bažnyčią viduje: sapno prasmės aiškinimas pagal įvairias svajonių knygas vyrams ir moterims Persimono sapno aiškinimas, kodėl sapne sapnuojate persimoną, kad sapne pamatytumėte persimoną kodėl

Persimono sapno aiškinimas, kodėl sapne sapnuojate persimoną, kad sapne pamatytumėte persimoną kodėl Užburta siela Karminių skaičių reikšmė

Užburta siela Karminių skaičių reikšmė