복합 트랜지스터(Darlington 및 Sziklai 회로). 적분 주입 논리의 논리 요소

7.2 트랜지스터 VT1

트랜지스터 VT1로서 우리는 트랜지스터 VT2와 동일한 동작점을 갖는 트랜지스터 KT339A를 사용합니다.

Rk = 100(옴)이라고 가정하겠습니다.

공식 5.1 - 5.13 및 7.1 - 7.3을 사용하여 특정 트랜지스터에 대한 등가 회로의 매개 변수를 계산해 보겠습니다.

Sk(요구)=Sk(통과)*=2×=1.41(pF), 여기서

Sk(필수)-주어진 Uke0에서 컬렉터 접합의 커패시턴스,

Sk(pasp)는 Uke(pasp)에서의 콜렉터 용량의 기준값입니다.

rb= =17.7(옴); gb==0.057(cm), 여기서

rb 기반 저항,

피드백 루프 상수의 기준 값입니다.

rе= ==6.54(옴), 여기서

재이미터 저항.

gbe===1.51(mS), 여기서

gbe-베이스-이미터 전도성,

공통 이미터 회로의 정적 전류 전달 계수의 기준 값입니다.

Ce===0.803(pF), 여기서

C는 이미 터 용량,

=1인 트랜지스터 차단 주파수의 ft 기준 값

Ri= =1000(옴), 여기서

Ri는 트랜지스터의 출력 저항이고,

Uke0(추가), Ik0(추가) - 각각 콜렉터의 허용 전압 정격 값과 콜렉터 전류의 일정 구성 요소입니다.

– 로딩 단계의 입력 저항 및 입력 커패시턴스.

상한 주파수는 각 단계의 왜곡이 0.75dB로 제공됩니다. 이 f 값은 기술 사양을 만족합니다. 수정이 필요하지 않습니다.

7.2.1 열 안정화 계획의 계산

7.1.1 단락에서 언급했듯이 이 증폭기에서는 KT339A 트랜지스터가 저전력이기 때문에 이미터 열 안정화가 가장 수용 가능하며 또한 이미터 안정화 구현도 쉽습니다. 이미터 열 안정화 회로는 그림 4.1에 나와 있습니다.

계산 절차:

1. 이미터 전압, 분배기 전류 및 공급 전압을 선택합니다.

2. 그럼 계산해보겠습니다.

분배기 전류는 트랜지스터의 기본 전류와 동일하도록 선택되며 다음 공식으로 계산됩니다.

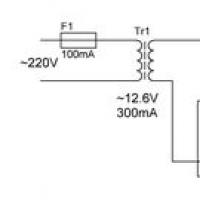

공급 전압은 다음 공식을 사용하여 계산됩니다. (V)

저항 값은 다음 공식을 사용하여 계산됩니다.

8. 입력 회로에 의한 왜곡

캐스케이드 입력 회로의 개략도가 그림 1에 나와 있습니다. 8.1.

그림 8.1 - 캐스케이드 입력 회로의 개략도

캐스케이드의 입력 임피던스가 병렬 RC 회로에 의해 근사화되면 고주파수 영역에서 입력 회로의 전송 계수는 다음 식으로 설명됩니다.

– 캐스케이드의 입력 저항 및 입력 커패시턴스.

입력 회로의 값은 식 (5.13)을 사용하여 계산되며, 여기에 값이 대체됩니다.

9. Cf, Rf, Cr 계산

증폭기 회로 다이어그램에는 4개의 커플링 커패시터와 3개의 안정화 커패시터가 포함되어 있습니다. 기술 사양에 따르면 펄스의 평평한 상단 왜곡은 5%를 넘지 않아야 합니다. 따라서 각 커플링 커패시터는 펄스의 평평한 상단을 0.71% 이하로 왜곡해야 합니다.

플랫톱 왜곡은 다음 공식을 사용하여 계산됩니다.

여기서 τ는 펄스 지속 시간입니다.

τn을 계산해 봅시다:

τn과 Cp는 다음과 같은 관계에 의해 관련됩니다:

여기서 R l, R p - 커패시턴스의 왼쪽과 오른쪽에 대한 저항입니다.

Cr을 계산해 봅시다. 첫 번째 단계의 입력 저항은 병렬 연결된 저항(입력 트랜지스터 Rb1 및 Rb2)의 저항과 같습니다.

R p =R in ||R b1 ||R b2 =628(옴)

첫 번째 단계의 출력 저항은 병렬 연결 Rк 및 트랜지스터 Ri의 출력 저항과 같습니다.

R1 =Rк||Ri=90.3(옴)

R p =R in ||R b1 ||R b2 =620(옴)

R l =Rк||Ri=444(옴)

R p =R in ||R b1 ||R b2 =48(옴)

R1 =Rк||Ri=71(옴)

R p =R n =75(옴)

여기서 C p1은 Rg와 첫 번째 단계 사이의 분리 커패시터이고, C 12 - 첫 번째와 두 번째 캐스케이드 사이, C 23 - 두 번째와 세 번째 캐스케이드 사이, C 3 - 최종 단계와 부하 사이입니다. 다른 모든 용기를 479∙10 -9 F에 배치함으로써 필요한 것보다 적은 양의 감소를 보장합니다.

R f 및 C f(U R Ф =1V)를 계산해 보겠습니다.

10. 결론

이 과정 프로젝트에서는 트랜지스터 2T602A, KT339A를 사용하여 펄스 증폭기를 개발했으며 다음과 같은 기술적 특성을 갖습니다.

상한 주파수 14MHz;

이득 64dB;

발전기 및 부하 저항 75Ω;

공급 전압 18V.

증폭기 회로는 그림 10.1에 나와 있습니다.

그림 10.1 - 증폭기 회로

앰프의 특성을 계산할 때 MathCad, Work Bench 소프트웨어를 사용했습니다.

문학

1. 반도체 장치. 중간 및 고전력 트랜지스터: 디렉토리 / A.A. Zaitsev, A.I. 미르킨, V.V. Mokryakov 및 기타 A.V. Golomedova.-M .: 라디오 및 통신, 1989.-640 p.

2. 바이폴라 트랜지스터를 사용하여 증폭기 스테이지의 고주파 보정 요소 계산. 무선 공학 전공 학생들을 위한 코스 설계에 관한 교육 및 방법론 매뉴얼 / A.A. 티토프, 톰스크: Vol. 상태 제어 시스템 및 무선전자공학 대학, 2002. - 45 p.

직접 작업합니다. 작업선은 Uke=Ek 및 Ik=Ek²Rn 점을 통과하여 출력 특성(베이스 전류) 그래프와 교차합니다. 펄스 증폭기를 계산할 때 최대 진폭을 달성하기 위해 최종 단계에 음의 펄스가 있으므로 작동 지점이 가장 낮은 전압에 가깝게 선택되었습니다. 출력 특성 그래프(그림 1)에 따르면 IKpost = 4.5mA, ... 값이 발견되었습니다.

Sf, Rf, Wed 계산 10. 결론 문헌 180학년 Kurmanov B.A. 학생을 위한 "원자력 발전소 회로" 분야의 과정 설계에 대한 기술 과제 2번. 프로젝트 주제: 펄스 증폭기 생성기 저항 Rg = 75Ω. 이득 K = 25dB. 펄스 지속 시간 0.5μs. 극성은 "긍정적"입니다. 듀티비 2. 정착 시간 25ns. 풀어 주다...

부하 저항과 일치시키기 위해서는 증폭 단계 후에 이미터 팔로워를 설치해야 하므로 증폭기 회로를 그려보겠습니다. 2.2 증폭기의 정적 모드 계산 첫 번째 증폭 단계를 계산합니다. 첫 번째 증폭기 단계의 동작점을 선택합니다. 그 특성:...

입력 신호 소스의 저항으로 인해 조사 중에 최적 조건이 변경되어도 노이즈가 추가로 증가하지 않습니다. IOU의 방사선 영향. AI가 IOU 매개변수에 미치는 영향. IOA(통합 연산 증폭기)는 범용 및 다기능 아날로그 클래스에 속하는 고품질 정밀 증폭기입니다.

예를 들어 트랜지스터를 사용하면 MJE3055T최대 전류는 10A이고 이득은 약 50에 불과하므로 완전히 열리려면 베이스에 약 200밀리암페어의 전류를 펌핑해야 합니다. 일반 MK 출력은 그 정도를 처리하지 못하지만, 이 200mA를 끌어낼 수 있는 약한 트랜지스터(일종의 BC337)를 연결하면 쉽습니다. 그러나 이것은 그가 알고 있는 것입니다. 즉석에서 만든 쓰레기로 제어 시스템을 만들어야 한다면 어떻게 될까요? 유용할 것입니다.

실제로는 기성품으로 트랜지스터 어셈블리. 외부적으로는 기존의 트랜지스터와 다르지 않습니다. 같은 몸, 같은 세 개의 다리. 전력이 많고 제어 전류가 미미하다는 것뿐입니다. :) 가격 목록에서는 일반적으로 Darlington 트랜지스터 또는 복합 트랜지스터와 같이 귀찮게 쓰지 않고 간단하게 씁니다.

예를 들어 커플 BDW93C(NPN) 및 BDW94С(PNP) 데이터시트의 내부 구조는 다음과 같습니다.

게다가, 달링턴 어셈블리. 여러 개를 한 번에 하나의 패키지에 포장하는 경우. 강력한 LED 디스플레이나 스테퍼 모터를 조종해야 할 때 없어서는 안 될 것입니다(). 이러한 빌드의 훌륭한 예 - 매우 인기 있고 쉽게 사용할 수 있음 ULN2003, 최대 드래그 가능 500 7개의 어셈블리 각각에 대해 mA입니다. 출력이 가능합니다 병렬로 포함전류 한도를 늘리려면 모든 입력과 출력이 병렬화될 경우 하나의 ULN은 전체적으로 최대 3.5A를 전달할 수 있습니다. 가장 좋은 점은 출구가 입구 반대편에 있어서 그 아래에 보드를 배치하는 것이 매우 편리하다는 것입니다. 곧장.

데이터시트에는 이 칩의 내부 구조가 나와 있습니다. 보시다시피 여기에는 보호 다이오드도 있습니다. 마치 연산 증폭기처럼 그려져 있음에도 불구하고 여기서의 출력은 오픈 컬렉터 형식입니다. 즉, 그는 접지에만 단락할 수 있습니다. 하나의 밸브 구조를 보면 동일한 데이터시트에서 무엇을 알 수 있습니까?

그림에서. 그림 2.16은 n 유형의 유도 채널(소위 n MIS 기술)이 있는 논리 요소의 다이어그램을 보여줍니다. 메인 트랜지스터 VT 1과 VT 2는 직렬로 연결되고 트랜지스터 VT 3은 부하 역할을 합니다. 요소의 두 입력 (x 1 = 1, x 2 = 1)에 고전압 U 1이 적용되는 경우 트랜지스터 VT 1과 VT 2가 모두 열리고 출력에 저전압 U 0이 설정됩니다. 다른 모든 경우에는 트랜지스터 VT 1 또는 VT 2 중 적어도 하나가 닫히고 전압 U 1이 출력에 설정됩니다. 따라서 요소는 논리적 AND-NOT 기능을 수행합니다.

그림에서. 그림 2.17은 OR-NOT 요소의 다이어그램을 보여줍니다. 입력 중 적어도 하나가 고전압 U 1 을 갖는 경우 출력에 저전압 U 0 이 설정되어 주 트랜지스터 VT 1 및 VT 2 중 하나가 열립니다.

그림에 표시됩니다. 2.18 다이어그램은 KMDP 기술의 NOR-NOT 요소에 대한 다이어그램입니다. 그 안에는 트랜지스터 VT 1과 VT 2가 주요 트랜지스터이고 트랜지스터 VT 3과 VT 4가 부하 트랜지스터입니다. 고전압 U 1을 보자. 이 경우 트랜지스터 VT 2는 열려 있고 트랜지스터 VT 4는 닫혀 있으며 다른 입력의 전압 레벨 및 나머지 트랜지스터의 상태에 관계없이 출력에 낮은 전압 U 0이 설정됩니다. 요소는 논리적 OR-NOT 연산을 구현합니다.

CMPD 회로는 전원 공급 장치의 전류 소비(따라서 전력)가 매우 낮다는 특징이 있습니다.

적분 주입 논리의 논리 요소

그림에서. 그림 2.19는 적분 주입 논리(I 2 L)의 논리 요소 토폴로지를 보여줍니다. 이러한 구조를 생성하려면 n형 전도성을 갖는 실리콘에서 두 가지 확산 단계가 필요합니다. 첫 번째 단계에서는 영역 p1 및 p2가 형성되고 두 번째 단계에서는 영역 n2가 형성됩니다.

요소의 구조는 p 1 -n 1 -p 2 -n 1 입니다. 이러한 4층 구조는 두 개의 기존 3층 트랜지스터 구조를 연결한 것으로 생각하면 편리합니다.

피 1 -N 1 -피 2 N 1 -피 2 -N 1

이 표현에 해당하는 다이어그램은 그림 2.20, a에 나와 있습니다. 이 구성표에 따른 요소의 작동을 고려해 봅시다.

유형 n 1 -p 2 -n 1 구조의 트랜지스터 VT 2는 여러 출력이 있는 인버터의 기능을 수행합니다(각 컬렉터는 개방형 컬렉터 회로에 따라 요소의 별도 출력을 형성함).

트랜지스터 VT 2라고 함 주사기는 p 1 -n 1 -p 2 와 같은 구조를 갖습니다. 이들 트랜지스터의 면적 n 1은 공통이므로, 트랜지스터 VT 2의 이미터는 트랜지스터 VT 1의 베이스에 연결되어야 합니다. 공통 영역 p 2가 있으면 트랜지스터 VT 2의 베이스를 트랜지스터 VT 1의 컬렉터와 연결해야 합니다. 이는 그림 2.20a에 표시된 대로 트랜지스터 VT 1과 VT 2 사이에 연결을 생성합니다.

트랜지스터 VT 1의 이미터는 양의 전위를 갖고 베이스는 0 전위에 있기 때문에 이미터 접합은 순방향 바이어스되고 트랜지스터는 개방됩니다.

이 트랜지스터의 컬렉터 전류는 트랜지스터 VT 3(이전 요소의 인버터) 또는 트랜지스터 VT 2의 이미터 접합을 통해 닫힐 수 있습니다.

이전 논리 요소가 열린 상태인 경우(트랜지스터 VT 3이 열려 있음) 이 요소의 입력에는 VT 2를 기반으로 작동하는 낮은 전압 레벨이 있어 이 트랜지스터를 닫힌 상태로 유지합니다. 인젝터 전류 VT 1은 트랜지스터 VT 3을 통해 닫힙니다. 이전 논리 요소가 닫히면(트랜지스터 VT 3이 닫힘) 인젝터 VT 1의 컬렉터 전류가 트랜지스터 VT 2의 베이스로 흐르고 이 트랜지스터는 열린 상태로 설정합니다.

따라서, VT 3이 닫히면 트랜지스터 VT 2가 열리고, 반대로 VT 3이 열리면 트랜지스터 VT 2가 닫힙니다. 요소의 열린 상태는 log.0 상태에 해당하고 닫힌 상태는 log.1 상태에 해당합니다.

인젝터는 직류(요소 그룹에 공통일 수 있음)의 소스입니다. 종종 그들은 그림 1에 제시된 요소의 기존 그래픽 지정을 사용합니다. 2.21, 나.

그림에서. 그림 2.21a는 OR-NOT 연산을 구현하는 회로를 보여줍니다. 요소 수집기의 연결은 소위 작동에 해당합니다. 설치 I. 실제로 요소 중 적어도 하나가 개방 상태(log.0 상태)이면 충분하며, 다음 요소의 인젝터 전류는 개방형 인버터를 통해 닫히고 낮은 log.0 레벨이 설정됩니다. 요소의 결합된 출력입니다. 결과적으로 이 출력에서는 논리식 x 1 · x 2에 해당하는 값이 형성됩니다. 여기에 드 모르간 변환을 적용하면 x 1 · x 2 = 이라는 표현이 나옵니다. 따라서 이러한 요소 연결은 실제로 OR-NOT 연산을 구현합니다.

논리 요소 AND 2 L에는 다음과 같은 장점이 있습니다.

높은 수준의 통합을 제공합니다. I 2 L 회로 제조에는 바이폴라 트랜지스터의 집적 회로 생산과 동일한 기술 프로세스가 사용되지만 기술 작업 수와 필요한 포토마스크 수는 더 적습니다.

감소된 전압이 사용됩니다(약 1V).

광범위한 성능에 걸쳐 전력을 교환할 수 있는 기능을 제공합니다(전력 소비는 수십 배로 변경될 수 있으며 이에 따라 성능이 변경됩니다).

TTL 요소와 잘 일치합니다.

그림에서. 그림 2.21b는 I 2 L 요소에서 TTL 요소로의 전환 다이어그램을 보여줍니다.

계열의 기본 논리 요소는 AND-NOT 논리 요소입니다. 그림에서. 그림 2.3은 세 가지 초기 NAND TTL 요소의 다이어그램을 보여줍니다. 모든 회로에는 세 가지 주요 단계가 포함됩니다: 트랜지스터 입력 VT1, 논리 AND 기능을 구현합니다. 위상 분리 트랜지스터 VT2푸시풀 출력단.

그림 2.3.a. K131 시리즈 기본 요소의 개략도

K131 시리즈 논리 요소의 작동 원리(그림 2.3.a)는 다음과 같습니다. 입력 중 하나에서 낮은 레벨 신호(0 - 0.4V)가 수신되면 멀티의 베이스-이미터 접합 - 이미 터 트랜지스터 VT1은 순방향 바이어스 (잠금 해제)되고 저항 R1을 통해 흐르는 거의 전체 전류가 접지로 분기되어 결과적으로 VT2가 닫히고 차단 모드에서 작동합니다. 저항 R2를 통해 흐르는 전류는 트랜지스터 VT3의 베이스를 포화시킵니다. 달링턴 회로에 따라 연결된 트랜지스터 VT3 및 VT4는 이미터 팔로워인 복합 트랜지스터를 형성합니다. 신호 전력을 증폭시키는 출력단 역할을 합니다. 회로의 출력에서 높은 논리 레벨 신호가 생성됩니다.

모든 입력에 하이 레벨 신호가 공급되면 다중 에미터 트랜지스터 VT1의 베이스-에미터 접합이 폐쇄 모드에 있습니다. 저항 R1을 통해 흐르는 전류는 트랜지스터 VT1의 베이스를 포화시키고, 그 결과 트랜지스터 VT5가 잠금 해제되고 논리 0 레벨이 회로 출력에 설정됩니다.

스위칭 트랜지스터 VT4 및 VT5가 열려 있고 이를 통해 큰 전류가 흐르기 때문에 제한 저항 R5가 회로에 도입됩니다.

VT2, R2 및 R3은 상 분리 캐스케이드를 형성합니다. 출력 n-p-n 트랜지스터를 하나씩 켜야 합니다. 캐스케이드에는 역위상 신호인 컬렉터와 이미터의 두 가지 출력이 있습니다.

다이오드 VD1 - VD3은 부정적인 충동으로부터 보호합니다.

그림 2.3.b, c. K155 및 K134 시리즈의 기본 요소에 대한 개략도

K155 및 K134 시리즈의 미세 회로에서 출력단은 비복합 리피터(트랜지스터만)에 구축됩니다. VT3) 및 포화 트랜지스터 VT5레벨 시프트 다이오드 도입으로 VD4(그림 2.3, b, c). 마지막 두 단계는 논리 NOT 연산을 구현하는 복잡한 인버터를 형성합니다. 두 개의 위상 분리 단계를 도입하면 OR-NOT 기능이 구현됩니다.

그림에서. 2.3, K131 시리즈의 기본 논리 요소(외국 아날로그 - 74N)를 보여줍니다. K155 시리즈(외국 아날로그 - 74)의 기본 요소가 그림 1에 나와 있습니다. 그림 2.3, b, a. 2.3, c - K134 시리즈 요소 (외국 아날로그 - 74L). 이제 이 시리즈는 사실상 개발되지 않았습니다.

초기 개발의 TTL 마이크로 회로는 내부 구조에 쇼트키 장벽과 접합부를 갖는 TTLSh 마이크로 회로로 적극적으로 대체되기 시작했습니다. 쇼트키 접합 트랜지스터(쇼트키 트랜지스터)는 잘 알려진 불포화 트랜지스터 스위치 회로를 기반으로 합니다(그림 2.4.a).

그림 2.4. 쇼트키 전이를 통해 구조를 얻는 원리에 대한 설명:

a - 불포화 트랜지스터 스위치; b - 쇼트키 다이오드를 갖는 트랜지스터; c - 쇼트키 트랜지스터의 상징.

트랜지스터가 포화되는 것을 방지하기 위해 콜렉터와 베이스 사이에 다이오드가 연결됩니다. 트랜지스터 포화를 제거하기 위해 피드백 다이오드를 사용하는 것은 B. N. Kononov에 의해 처음 제안되었으나 이 경우 1V까지 증가할 수 있습니다. 이상적인 다이오드는 쇼트키 배리어 다이오드입니다. 금속과 가볍게 도핑된 n형 반도체 사이에 형성된 접점입니다. 금속에서는 전자 중 일부(원자가대 외부의 전자)만 자유로워집니다. 반도체에서는 불순물 원자가 추가되어 생성된 전도 경계에 자유 전자가 존재합니다. 바이어스 전압이 없으면 양쪽 장벽을 통과하는 전자의 수가 동일합니다. 즉, 전류가 없습니다. 순방향 바이어스 시 전자는 전위 장벽을 넘어 금속으로 들어갈 수 있는 에너지를 갖습니다. 바이어스 전압이 증가함에 따라 장벽 폭은 감소하고 순방향 전류는 급격히 증가합니다.

역방향 바이어스 시, 반도체의 전자는 전위 장벽을 극복하기 위해 더 많은 에너지를 필요로 합니다. 금속 내의 전자의 경우 전위 장벽은 바이어스 전압에 의존하지 않으므로 작은 역전류가 흐르고 눈사태 항복이 발생할 때까지 실질적으로 일정하게 유지됩니다.

쇼트키 다이오드의 전류는 다수 캐리어에 의해 결정되므로 동일한 순방향 바이어스에서 더 크므로 쇼트키 다이오드의 순방향 전압 강하는 주어진 전류에서 기존 p-n 접합보다 적습니다. 따라서, 쇼트키 다이오드는 기존 실리콘 다이오드의 문턱 전압이 0.7V인 것에 비해 (0.2-0.3)V 정도의 문턱 개방 전압을 가지며, 반도체 내 소수 캐리어의 수명을 크게 단축시킨다.

그림의 다이어그램에서. 2.4, b 트랜지스터 VT1개방 임계값(0.2...0.3)V가 낮은 Shatky 다이오드에 의해 포화 상태가 되는 것을 방지하므로 포화된 트랜지스터에 비해 전압이 약간 증가합니다. VT1. 그림에서. 2.4, c는 "쇼트키 트랜지스터"를 사용한 회로를 보여줍니다. 쇼트키 트랜지스터를 기반으로 두 가지 주요 TTLSh 시리즈의 미세 회로가 생산되었습니다(그림 2.5).

그림에서. 2.5, K531 시리즈의 마이크로 회로 (외국 아날로그 - 74S)의 기초로 사용되는 고속 논리 요소의 다이어그램을 보여줍니다 (S는 독일 물리학 자 Schottky 성의 첫 글자입니다). 이 요소에서는 트랜지스터로 만들어진 위상 분리 캐스케이드의 이미 터 회로 VT2, 전류 발생기가 켜집니다 - 트랜지스터 VT6저항기로 R4그리고 R5. 이를 통해 논리 요소의 성능을 높일 수 있습니다. 그 외에는 이 논리 요소는 K131 시리즈의 기본 요소와 유사합니다. 그러나 쇼트키 트랜지스터의 도입으로 비용 절감이 가능해졌습니다. tzd.r두 배.

그림에서. 2.5, b는 K555 시리즈(외국 아날로그 - 74LS)의 기본 논리 요소 다이어그램을 보여줍니다. 이 회로에서는 다중 이미터 트랜지스터 대신 쇼트키 다이오드 매트릭스가 입력에 사용됩니다. Shatky 다이오드를 도입하면 과도한 기본 전하의 축적을 제거하여 트랜지스터의 턴오프 시간을 늘리고 온도 범위에서 스위칭 시간의 안정성을 보장합니다.

출력단 상단의 저항 R6은 트랜지스터 베이스에 필요한 전압을 생성합니다. VT3그것을 열려면. 게이트가 닫혀 있을 때 전력 소모를 줄이기 위해(), 저항 R6공통 버스가 아닌 요소의 출력에 연결하십시오.

다이오드 VD7, 직렬로 연결됨 R6위상 분리 캐스케이드의 콜렉터 부하 저항과 병렬 R2, 부하 커패시턴스에 저장된 에너지의 일부를 사용하여 트랜지스터 콜렉터 전류를 증가시켜 회로의 켜기 지연을 줄일 수 있습니다. VT1전환 모드에서.

트랜지스터 VT3능동 모드(이미터 팔로워)에서 작동하므로 쇼트키 다이오드 없이 구현됩니다.

복합 트랜지스터(Darlington 트랜지스터) - 두 개 이상의 바이폴라 트랜지스터를 결합하여 전류 이득을 높입니다. 이러한 트랜지스터는 높은 전류로 작동하는 회로(예: 전압 안정기 회로, 전력 증폭기의 출력단)와 높은 입력 임피던스를 제공해야 하는 경우 증폭기의 입력단에 사용됩니다.

복합 트랜지스터의 기호

복합 트랜지스터에는 3개의 단자(베이스, 이미터, 컬렉터)가 있으며 이는 기존 단일 트랜지스터의 단자와 동일합니다. 일반적인 복합 트랜지스터(때때로 "슈퍼베타"라고도 함)의 전류 이득은 고전력 트랜지스터의 경우 1000, 저전력 트랜지스터의 경우 50,000입니다. 이는 작은 베이스 전류만으로도 복합 트랜지스터를 켜기에 충분하다는 의미입니다.

바이폴라 트랜지스터와 달리 전계 효과 트랜지스터는 복합 연결에 사용되지 않습니다. 전계 효과 트랜지스터는 이미 입력 전류가 매우 낮기 때문에 결합할 필요가 없습니다. 그러나 전계 효과 트랜지스터와 바이폴라 트랜지스터를 함께 사용하는 회로(예: 절연 게이트 바이폴라 트랜지스터)가 있습니다. 어떤 의미에서 이러한 회로는 복합 트랜지스터로 간주될 수도 있습니다. 복합 트랜지스터와 동일베이스의 두께를 줄여 이득값을 높이는 것이 가능하지만 이는 기술적 어려움을 안겨준다.

예 슈퍼베타(super-β)트랜지스터는 KT3102, KT3107 시리즈에서 사용할 수 있습니다. 그러나 Darlington 구성표를 사용하여 결합할 수도 있습니다. 이 경우 기본 바이어스 전류는 50pA와 동일하게 만들 수 있습니다(이러한 회로의 예로는 LM111 및 LM316과 같은 연산 증폭기가 있습니다).

복합 트랜지스터를 사용한 일반적인 증폭기 사진

달링턴 서킷

이러한 트랜지스터의 한 유형은 전기 기술자 Sidney Darlington이 발명했습니다.

복합 트랜지스터의 개략도

복합 트랜지스터는 이전 단계의 이미터의 부하가 다음 단계의 트랜지스터의 베이스-이미터 전이, 즉 트랜지스터가 컬렉터로 연결되는 방식으로 연결된 여러 트랜지스터의 캐스케이드 연결입니다. 입력 트랜지스터의 이미터는 출력 트랜지스터의 베이스에 연결됩니다. 또한 첫 번째 트랜지스터의 저항성 부하를 회로의 일부로 사용하여 폐쇄를 가속화할 수 있습니다. 이러한 연결은 전체적으로 하나의 트랜지스터로 간주되며, 트랜지스터가 활성 모드에서 작동할 때 전류 이득은 첫 번째 및 두 번째 트랜지스터 이득의 곱과 거의 같습니다.

β с = β 1 ∙ β 2

복합 트랜지스터가 실제로 계수를 가지고 있음을 보여 드리겠습니다.β , 두 구성 요소보다 훨씬 큽니다. 증분 설정디엘비= 디엘b1, 우리는 다음을 얻습니다:

디엘e1 = (1 + β 1) ∙ d엘비= 디엘b2

디엘에게= 디엘k1+ 디엘k2= β 1 ∙ d엘비+ β 2 ∙ ((1 + β 1) ∙ d엘비)

나누는 디내가~에 DL비, 결과 차동 전송 계수를 찾습니다.

β Σ = β 1 + β 2 + β 1 ∙ β 2

왜냐면 항상β >1 , 이는 다음과 같이 고려될 수 있습니다:

β Σ = β 1 ∙ β 1

계수가 중요하다는 점을 강조해야 합니다.β 1 그리고 β 1 동일한 유형의 트랜지스터의 경우에도 이미터 전류가 다를 수 있습니다.나는 e2 V 1 + β 2이미터 전류의 곱나는 e1(이것은 명백한 평등에서 비롯됩니다.나는 b2 = 나는 e1).

시클라이 계획

Darlington 쌍은 발명가 George Sziklai의 이름을 딴 Sziklai 트랜지스터 연결과 유사하며 때로는 보완적인 Darlington 트랜지스터라고도 합니다. 동일한 전도성 유형의 두 개의 트랜지스터로 구성된 Darlington 회로와 달리 Sziklai 회로에는 서로 다른 극성의 트랜지스터가 포함되어 있습니다. p – n – p 및 n – p – n ). Siklai 부부는 다음과 같이 행동합니다. n–p–n - 고이득 트랜지스터. 입력 전압은 트랜지스터 Q1의 베이스와 이미터 사이의 전압이고, 포화 전압은 적어도 다이오드 양단의 전압 강하와 같습니다. 트랜지스터 Q2의 베이스와 이미터 사이에 낮은 저항 저항을 포함하는 것이 좋습니다. 이 회로는 동일한 극성의 출력 트랜지스터를 사용할 때 강력한 푸시풀 출력단에 사용됩니다.

Sziklai 캐스케이드, 트랜지스터와 유사 n – p – n 전환

캐스코드 회로

소위 캐스코드 회로에 따라 만들어진 복합 트랜지스터는 트랜지스터 VT1이 공통 이미터가 있는 회로에 연결되고 트랜지스터 VT2가 공통 베이스가 있는 회로에 연결된다는 사실이 특징입니다. 이러한 복합 트랜지스터는 공통 이미터 회로에 연결된 단일 트랜지스터와 동일하지만 부하에서 훨씬 더 나은 주파수 특성과 더 큰 왜곡되지 않은 전력을 가지며 밀러 효과(등가 정전 용량의 증가)를 크게 줄일 수도 있습니다. 이 요소가 꺼졌을 때 이 요소의 출력에서 입력으로의 피드백으로 인해 증폭기 요소 반전).

복합 트랜지스터의 장점과 단점

복합 트랜지스터의 높은 이득 값은 정적 모드에서만 구현되므로 복합 트랜지스터는 연산 증폭기의 입력단에 널리 사용됩니다. 고주파수 회로에서 복합 트랜지스터는 더 이상 이러한 이점을 갖지 않습니다. 전류 증폭의 제한 주파수와 복합 트랜지스터의 작동 속도는 각 트랜지스터 VT1 및 VT2에 대한 동일한 매개 변수보다 낮습니다.

장점:

ㅏ)높은 전류 이득.

비)달링턴 회로는 집적 회로 형태로 제조되며 동일한 전류에서 실리콘의 작업 표면은 바이폴라 트랜지스터의 작업 표면보다 작습니다. 이 회로는 고전압에서 큰 관심을 끌고 있습니다.

결점:

ㅏ)낮은 성능, 특히 열린 상태에서 닫힌 상태로의 전환. 이러한 이유로 복합 트랜지스터는 주로 저주파 키 및 증폭기 회로에 사용되며 고주파수에서는 해당 매개변수가 단일 트랜지스터의 매개변수보다 나쁩니다.

비)달링턴 회로의 베이스-이미터 접합에 걸친 순방향 전압 강하는 기존 트랜지스터보다 거의 두 배 크며, 실리콘 트랜지스터의 경우 약 1.2 - 1.4V입니다(pn 접합에서 전압 강하의 두 배보다 작을 수 없음). .

V)실리콘 트랜지스터의 경우 저전력 트랜지스터의 경우 약 0.9V(기존 트랜지스터의 경우 0.2V), 고전력 트랜지스터의 경우 약 2V(pn 접합의 전압 강하보다 낮을 수 없음)의 높은 콜렉터-이미터 포화 전압 포화된 입력 트랜지스터의 전압 강하).

부하 저항 R1을 사용하면 복합 트랜지스터의 일부 특성을 향상시킬 수 있습니다. 저항 값은 닫힌 상태에서 트랜지스터 VT1의 콜렉터-이미터 전류가 트랜지스터 VT2를 여는 데 불충분한 저항 양단의 전압 강하를 생성하는 방식으로 선택됩니다. 따라서, 트랜지스터 VT1의 누설 전류는 트랜지스터 VT2에 의해 증폭되지 않으며, 그에 따라 오프 상태에서 복합 트랜지스터의 총 콜렉터-이미터 전류를 감소시킨다. 또한 저항 R1을 사용하면 트랜지스터 VT2를 강제로 닫아 복합 트랜지스터의 속도를 높이는 데 도움이 됩니다. 일반적으로 R1의 저항은 고전력 달링턴 트랜지스터에서 수백 옴이고 소신호 달링턴 트랜지스터에서 수 k옴입니다. 이미터 저항이 있는 회로의 예로는 강력한 n-p-n Darlington 트랜지스터 유형 KT825가 있으며, 전류 이득은 10A의 콜렉터 전류에 대해 10,000(일반 값)입니다.

히로시마와 나가사키를 폭격한 조종사들의 이야기

히로시마와 나가사키를 폭격한 조종사들의 이야기 원활한 용량 충전, 무엇을 선택할 것인가?

원활한 용량 충전, 무엇을 선택할 것인가? 소규모 수학 학부

소규모 수학 학부 “꿈에서 둥근 춤을 꿈꾸는 이유는 무엇입니까?

“꿈에서 둥근 춤을 꿈꾸는 이유는 무엇입니까? 내부 교회에 대한 꿈을 꾸는 이유 : 남성과 여성을위한 다양한 꿈 책에 따른 꿈의 의미 해석

내부 교회에 대한 꿈을 꾸는 이유 : 남성과 여성을위한 다양한 꿈 책에 따른 꿈의 의미 해석 감꿈해몽, 감꿈해몽, 감꿈해몽, 감꿈해몽

감꿈해몽, 감꿈해몽, 감꿈해몽, 감꿈해몽 마법에 걸린 영혼 카르마 숫자의 의미

마법에 걸린 영혼 카르마 숫자의 의미